Grobe Erklärung & Einführung

Was ist VHDL?

- VHDL steht für VHSIC (Very High Speed Integrated Circuit) Hardware Description Language und ist eine Sprache zur Beschreibung digitaler Schaltungen.

- Sie wird genutzt, um das Verhalten und die Struktur von Schaltungen textuell zu modellieren.

- Mit VHDL kann man Schaltungen nicht nur entwerfen, sondern auch simulieren und testen.

Warum VHDL?

- Statt einzelne Bauteile wie Logikgatter zu verdrahten, beschreibt man in VHDL, was und wie die Schaltung funktioniert.

- Die textuelle Beschreibung wird von Synthesetools in echte Hardware umgesetzt (z.B. auf FPGAs).

- VHDL eignet sich besonders für modulare und wiederverwendbare Designs.

Was kann man mit VHDL machen?

- Strukturelle Beschreibung: Wie sind Bauteile miteinander verbunden?

- Verhaltensbeschreibung: Wie reagiert die Schaltung auf bestimmte Eingaben?

- Simulation: Testen des Designs, bevor es in Hardware umgesetzt wird.

Einsatzgebiete:

- Digitale Elektronik

- FPGA-Programmierung

- Lehre und Forschung

- Entwicklung komplexer digitaler Systeme

Unterschied von VHDL zu Programmiersprachen

VHDL ist eine Hardwarebeschreibungssprache, die zur Modellierung digitaler Systeme verwendet wird. In diesem Tutorial lernst du die Grundlagen von VHDL kennen.

Der fundamentale Unterschied:

| Merkmal | VHDL (Hardwarebeschreibungssprache, HDL) | Klassische Programmiersprachen (z.B. C++, Python) |

|---|---|---|

| Ziel | Beschreibung und Modellierung der Struktur und des Verhaltens von digitalen Schaltungen (Hardware), z.B. für FPGAs oder ASICs(FPGA und ASIC sind beides Arten von integrierten Schaltkreisen (Chips), die zur Implementierung digitaler Schaltungen verwendet werden.). | Beschreibung einer sequenziellen Abfolge von Anweisungen zur Ausführung auf einem Prozessor (Software). |

| Ergebnis | Ein Hardware-Netzwerk aus Logikgattern, Speichern und Verbindungen, das durch ein Synthesewerkzeug aus dem Code erzeugt wird. | Eine ausführbare Datei (Programm), die von einem Prozessor interpretiert oder direkt ausgeführt wird. |

1. Parallelität vs. Sequenzialität

- VHDL: Intrinsische Parallelität Der Code beschreibt Komponenten und Prozesse, die gleichzeitig (parallel) ablaufen. Wenn Sie in VHDL zwei Prozesse definieren, laufen diese – analog zu den physikalischen Schaltungsteilen – gleichzeitig. Der Datenfluss und die gleichzeitige Signalverarbeitung stehen im Vordergrund.

- Programmiersprachen: Sequenzielle Ausführung Der Code wird normalerweise Anweisung für Anweisung in einer festen Reihenfolge abgearbeitet (sequenziell), wie es von der CPU vorgegeben wird.

2. Zeit und Signale

- VHDL: VHDL arbeitet mit Signalen und expliziten Zeitverzögerungen. Signale repräsentieren physikalische Drähte in der Schaltung, deren Wert sich erst nach einer bestimmten Zeitverzögerung (oder im nächsten Taktzyklus) ändert. Die zeitliche Komponente ist fundamental.

- Programmiersprachen: Sie verwenden Variablen, deren Wert sich sofort ändert. Die Programmausführung ist primär logisch sequenziell und die Laufzeit wird in der Regel nicht explizit in der Sprache definiert (abgesehen von Funktionen zur Zeitmessung oder Verzögerung).

3. Synthese vs. Kompilierung

- VHDL: Der VHDL-Code wird nicht kompiliert, um auf einem Prozessor zu laufen, sondern synthetisiert. Das Synthesewerkzeug wandelt die textuelle Beschreibung in eine Netzliste um, die die tatsächliche physische Hardware-Implementierung (Gatter, Flip-Flops etc.) beschreibt.

- Programmiersprachen: Der Code wird kompiliert oder interpretiert, um Maschinencode zu erzeugen, der auf einem Prozessor läuft.

Der Detail-Unterschied(Syntax unterschied):

| Merkmal | VHDL | Klassische P-Sprachen |

|---|---|---|

| Zuweisung 1 (Signal) | Signal <= Wert; (Nicht sofort; modelliert Hardware-Verzögerung) | Variable = Wert; (Sofortige Zuweisung) |

| Zuweisung 2 (Variable) | Variable := Wert; (sofort; nur in sequenziellen Blöcken) | Variable = Wert; (Sofortige Zuweisung) |

| Typen | Spezielle Hardware-Typen wie std_logic (9 Zustände, z.B. 'Z' für Hochimpedanz). | Meist nur Boolean (true/false) und Standard-Zahlentypen. |

Aufbau von VHDL

VHDL (Very High Speed Integrated Circuit Hardware Description Language) ist eine Hardwarebeschreibungssprache, mit der digitale Systeme wie Schaltungen und Prozessoren textbasiert modelliert, simuliert und synthetisiert werden können.

1. Bibliotheken und Pakete

- Am Anfang werden Bibliotheken eingebunden (z. B. IEEE) und Pakete ausgewählt, die Datentypen und Funktionen bereitstellen.

2. Entity (Schnittstelle)

- Die Entity beschreibt die äußere Schnittstelle eines Moduls.

- Hier werden Ports definiert: Eingänge, Ausgänge und deren Datentypen.

3. Architecture (Verhalten/Struktur)

- Die Architecture beschreibt das Innenleben des Moduls.

- Es gibt zwei Hauptarten:

- Verhaltensbeschreibung (Behavioral): beschreibt, was das Modul tun soll, meist mit Prozessen und Anweisungen.

- Strukturbeschreibung (Structural): beschreibt, wie das Modul aus anderen Komponenten zusammengesetzt ist.

4. Konfiguration (optional)

- Mit einer Konfiguration kann festgelegt werden, welche Architecture zu einer Entity verwendet wird.

- Wird oft nur bei komplexeren Projekten benötigt.

5. Testbench (Simulation)

- Eine Testbench ist ein spezielles VHDL-Modul, das Eingaben erzeugt und Ausgaben überprüft, um das Verhalten der Schaltung zu testen.

- Sie hat keine Ports, sondern simuliert die Umgebung.

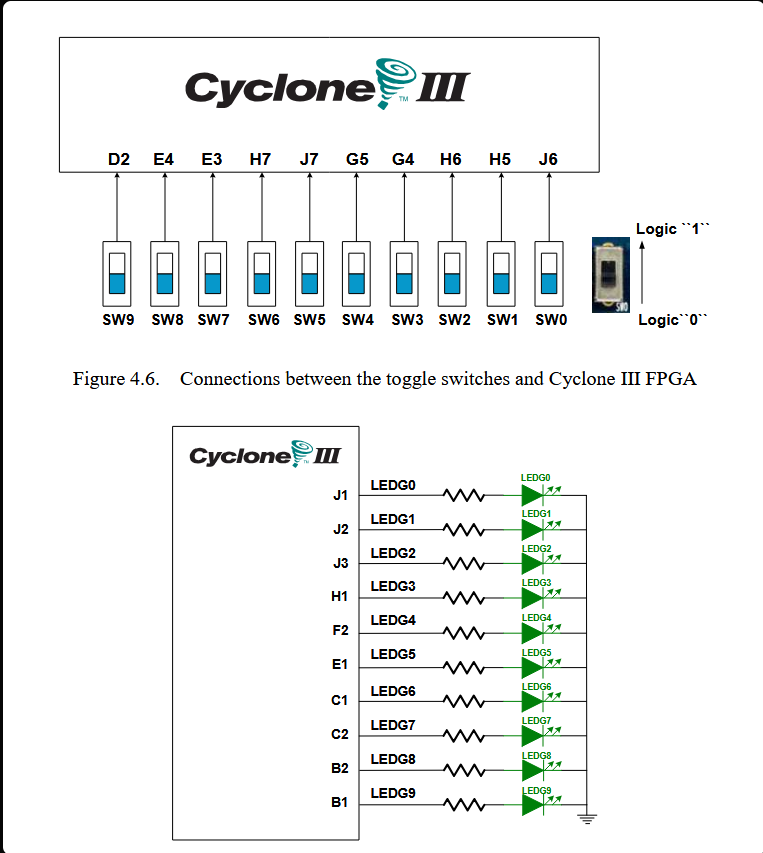

Anschlüsse und Elemente des DE0-Boards

- LEDs (10) – Ausgaben

- Schalter (10) – Eingaben

- Taster (4) – Eingaben (Impuls)

- 7-Segment-Anzeigen (4) – Zahlendarstellung

- GPIO-Header – externe Module/Sensoren

- ADC-Eingänge – analoge Signale

- SD-Karten-Slot – Datenspeicherung

- Speicher (SRAM, SDRAM, Flash) – komplexere Designs

- USB-Blaster – Programmierung & Debug

Nutzung mit VHDL

- Clock: Standardtakt ist 50 MHz. Meist wird er mit einem Clock-Divider heruntergeteilt, um sichtbare Effekte (z. B. LED-Blinken) zu erzeugen.

- Pin-Zuordnung: In Quartus müssen die Signale aus dem VHDL-Code den richtigen Pins des Boards zugewiesen werden.

- Workflow:

- VHDL-Code schreiben

- Kompilieren in Quartus

- Bitstream (.sof) erzeugen

- Mit USB-Blaster ins Board laden

Pin Belegung

Installation Quartus II

Hier wird erklärt, wie du die Quartus II Web Edition installierst, um mit VHDL-Entwicklung zu beginnen.

Vorbereitung

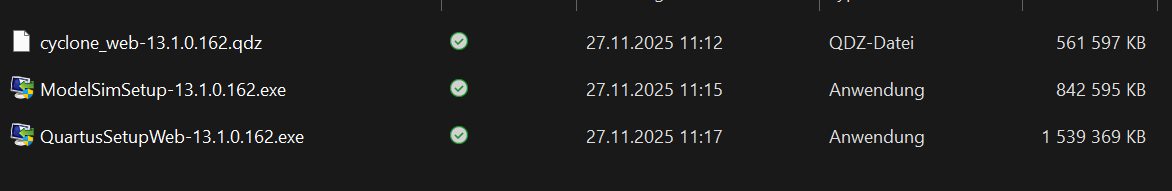

Zuerst müssen folgende 3 Dateien heruntergeladen werden:

Alternativ: Vom Schulserver herunterladen

Die gleichen Dateien sind auf dem Schulserver verfügbar:

Danach müssen alle 3 Dateien in das gleiche Verzeichnis gespeichert werden:

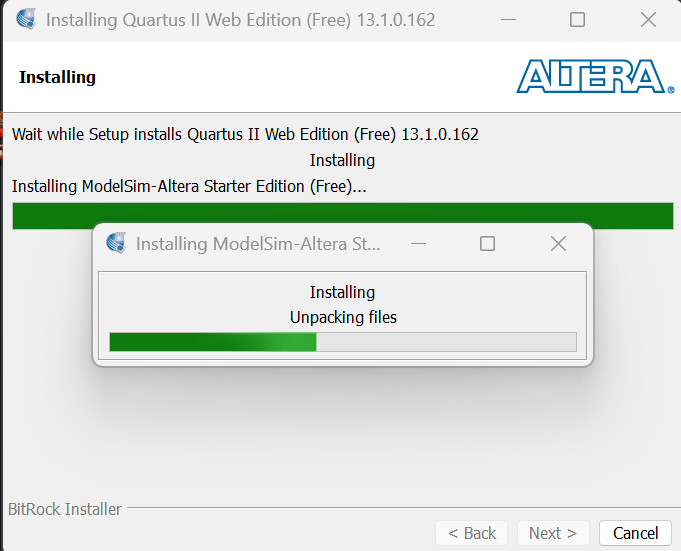

Installation von Quartus II und ModelSim

- Doppelklicke auf die Datei QuartusSetupWeb-13.1.0.162.exe und installiere das Programm.

- Doppelklicke anschließend auf die Datei ModelSimSetup-13.1.0.162.exe und installiere ebenso dieses Programm.

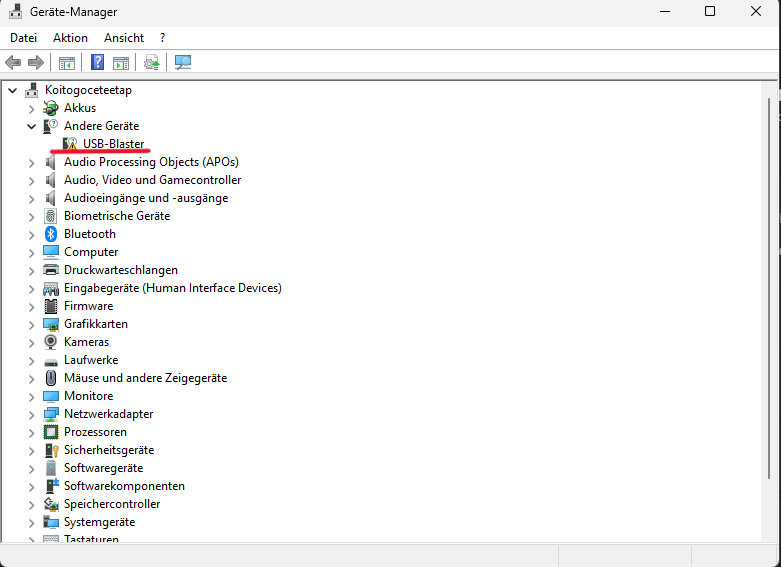

Installation des USB Blaster Treibers

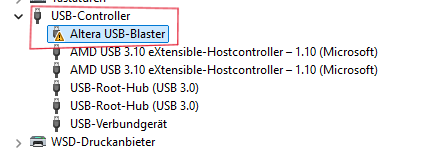

- Öffne den Geräte Manager und doppelklicke unter Andere Geräte auf USB Blaster

- Klicke in Eigenschaften von USB-Blaster unter Allgemein auf Treiber aktualisieren

- Klicke anschließend auf Auf meinem Computer nach Treibern suchen

- Klicke auf Durchsuchen und suche nach dem Ordner in dem der USB-Blaster Treiber installiert ist

- Klicke anschließend auf Weiter und dann auf Installieren

- Danach sollte unter USB-Controller der Altera USB-Blaster zu sehen sein

- Zuletzt ist ein Neustart erforderlich!

Erstes Projekt anlegen

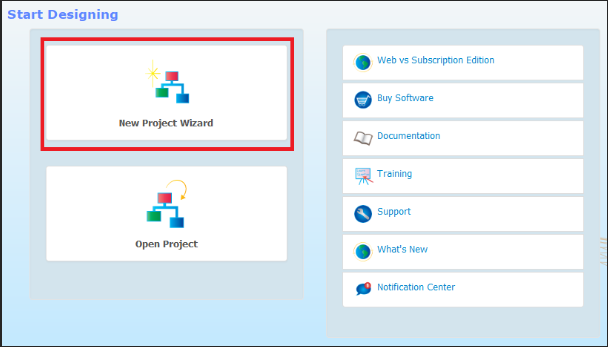

- Programm Quartus öffnen und auf New Project Wizard klicken.

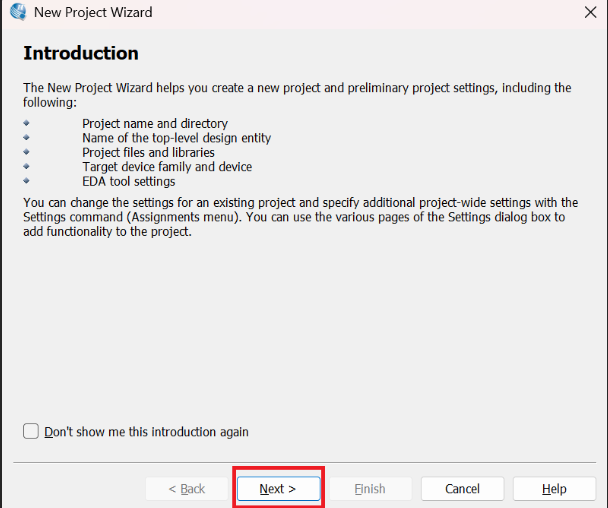

- Hier auf Next klicken.

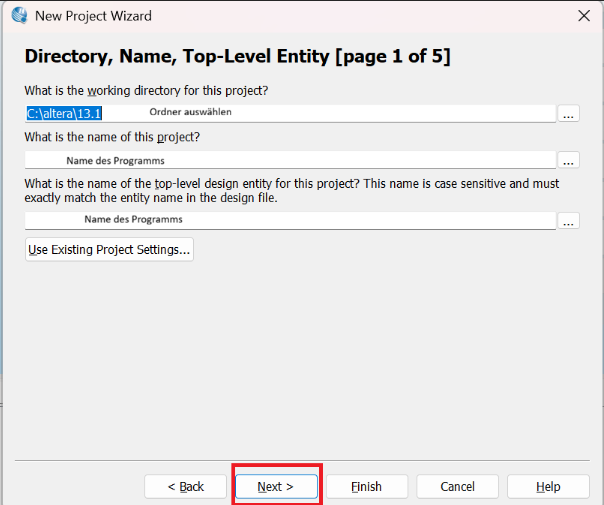

- Ganz oben den Ordner auswählen zum speichern. In der Zeile darunter den Namen des Projektes angeben und wieder in der Zeile drunter sollte normalerweise automatisch stehen. Zum Schluss wieder auf Next klicken.

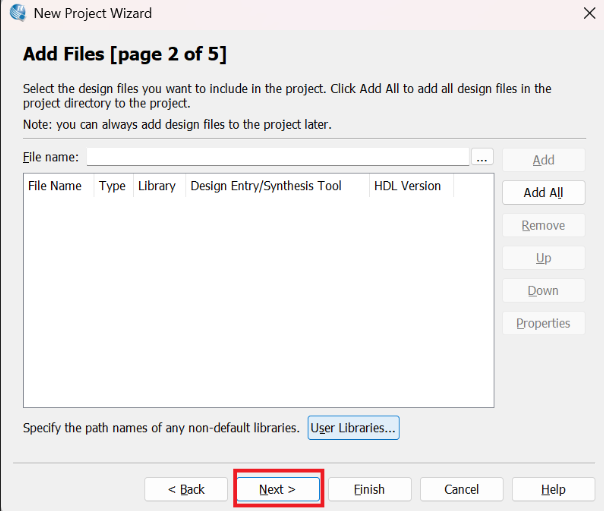

- Auf dieser Seite ist nichts zum Einstellen da einfach auf Next

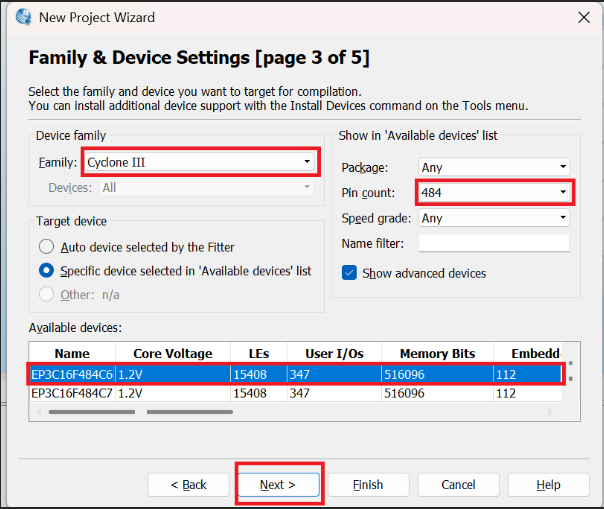

- Auf dieser Seite muss man bei der Familie den Cyclone III auswählen Bei den Pin count muss man die Zahl 484 einstellen Bei den Available devices ist der Namen EP3C16F484C6 auszuwählen

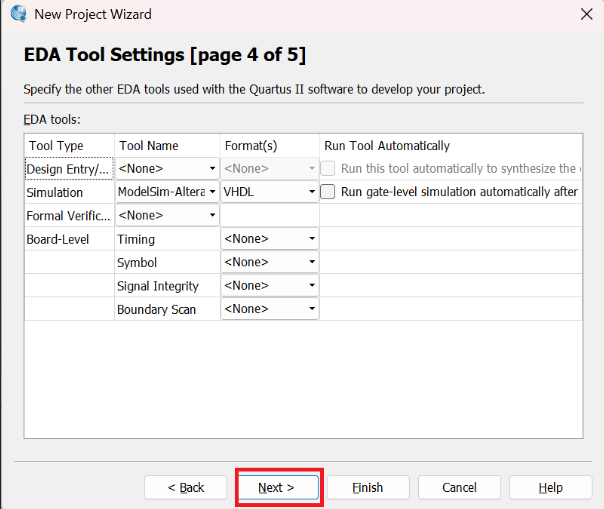

- Auf dieser Seite muss man nichts einstellen und einfach auf Next drücken.

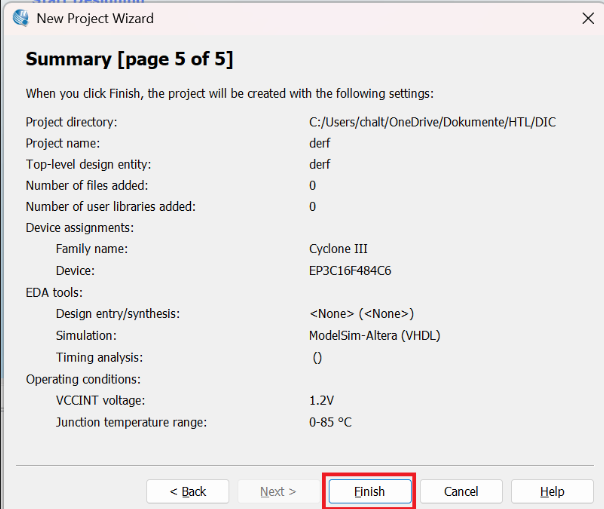

- Auf der 5. Seite einfach auf Finish drücken

Um weiterzuarbeiten die folgenden Schritte befolgen, die hier erklärt sind:

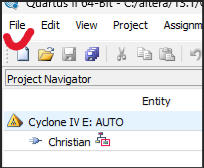

- Nach dem Erstellen des Projekts auf FILE drücken

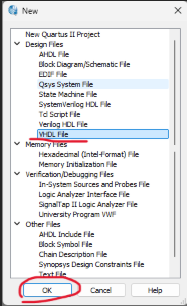

- Auf NEW klicken

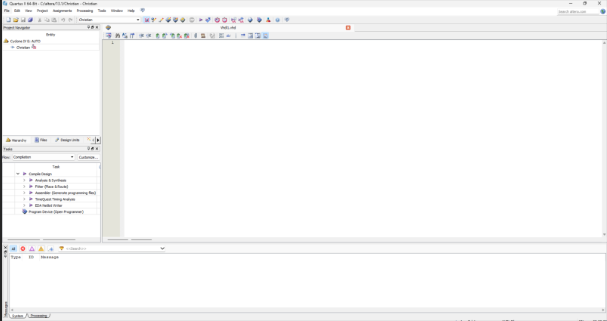

- Zum Schluss sollte es dann so aussehen

- Hier den VHDL-Code einfügen

- Als nächstes den Pinplaner öfffnen und die Pins zuweisen

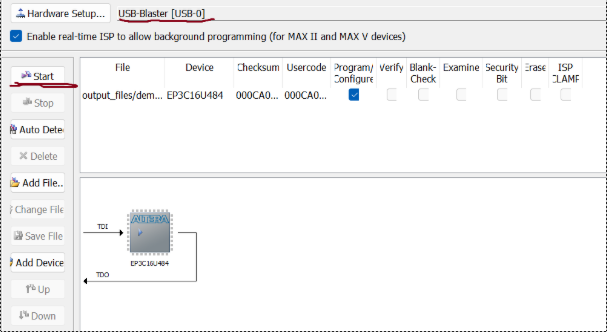

- Als nächstes den Programmer öffnen

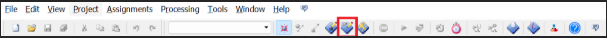

- Dann auf Start drücken

- Wenn alles geklapt hat sollte oben in der rechten Ecke der Balken grün sein und so aussehen

Demo Projekt am DE0-Board

Das Demo Projekt läuft sobald man das DE0-Board anschließt und sieht wie folgt aus:

Aufbau von ASICs – PROM, PAL & GAL

ASIC bedeutet Application Specific Integrated Circuit, also ein integrierter Schaltkreis für eine spezielle Aufgabe. PROM, PAL und GAL gehören zu den programmierbaren Logikbausteinen und sind frühe bzw. klassische Formen von ASICs.

️1. PROM (Programmable Read-Only Memory)

Ein PROM ist ein Speicherbaustein, der einmalig programmiert werden kann und später nur noch gelesen wird. Er kann aber auch zur Realisierung von Logikfunktionen genutzt werden.

Aufbau eines PROM:

Ein PROM besteht aus:

- Adressdecoder (UND-Ebene)

- Feste (ODER-Ebene)

- Programmierbare Speicherstellen (Sicherungen / Fuses)

Funktionsprinzip:

- Die Eingänge bilden eine Adresse.

- Der Adressdecoder schaltet genau eine Speicherzelle frei.

- Über programmierbare Sicherungen (Fuses) wird festgelegt, ob am Ausgang eine 0 oder 1 erscheint.

Besonderheiten:

- UND-Ebene: fest

- ODER-Ebene: fest

- Nur die Speicherstellen sind programmierbar

- Sehr sicher, aber nicht änderbar

PROM eignet sich gut für Wahrheitstabellen mit vielen Eingängen.

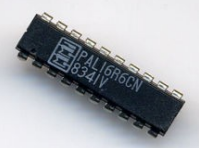

2. PAL (Programmable Array Logic)

Ein PAL ist ein frei programmierbarer Logikbaustein zur Realisierung kombinatorischer Logik.

Aufbau eines PAL:

Ein PAL besteht aus:

- Programmierbare UND-Ebene

- Feste ODER-Ebene

- Ausgangsstufe (optional mit Flipflop)

Funktionsprinzip:

- Die Eingänge gehen in eine UND-Matrix

- Dort werden Produktterme gebildet

- Diese werden in einer festen ODER-Ebene zusammengefasst

- Das Ergebnis erscheint am Ausgang

Besonderheiten:

- UND-Ebene: programmierbar

- ODER-Ebene: fest

- Schnell, einfach, preiswert

- Begrenzte Flexibilität

3. GAL (Generic Array Logic)

Ein GAL ist die moderne Weiterentwicklung des PAL.

Aufbau eines GAL:

- Programmierbare UND-Ebene

- Programmierbare ODER-Ebene

- Flexible Ausgangszellen

- Direkt

- Invertiert

- Mit Flipflop

- EEPROM-Technik (wiederbeschreibbar)

Besonderheiten:

- UND-Ebene: programmierbar

- ODER-Ebene: programmierbar

- Löschbar & neu programmierbar

- Ein GAL kann mehrere PAL-Typen ersetzen

- Sehr flexibel

FPGA

Was ist ein FPGA?

Ein FPGA (Field Programmable Gate Array) ist ein integrierter Schaltkreis, dessen innere Struktur nach der Herstellung frei programmiert werden kann. Das bedeutet: Du kannst selbst bestimmen, welche digitale Schaltung im Chip entsteht.

Wie ist ein FPGA aufgebaut?

Ein FPGA besteht aus vielen kleinen, universellen Bausteinen:

1. Logikzellen (CLBs – Configurable Logic Blocks)

Der Grundbaustein jedes FPGAs.

Jeder Block enthält:

- LUTs (Look-Up Tables) → erzeugen Logikfunktionen (AND, OR, XOR, Addierer, …)

- Flip-Flops → speichert 1 Bit, ermöglicht Register

2. Programmierbare Verbindungen (Routing-Netzwerk)

Ein riesiges Gitter aus schaltbaren Leitungen.

Damit kannst du Logikzellen miteinander verbinden → wie Drähte.

3. IO-Blöcke

Schnittstellen nach außen:

- digitale Pins

- oft konfigurierbar für verschiedene Spannungen (1,2–3,3V)

- manchmal High-Speed-Transceiver

Wie funktioniert ein FPGA?

Wichtig:

Ein FPGA führt kein Programm aus – es IST die Schaltung.

Wenn du ein FPGA programmierst, passiert Folgendes:

- Du beschreibst, welche Logik du willst (z. B. einen Zähler).

- Die Software baut daraus:

- Gatter

- Register

- Multiplexer

- Verbindungen

- Die Struktur wird als Bitstream erzeugt.

- Dieser Bitstream wird ins FPGA geladen.

- Das FPGA wird physisch in diese Schaltung verwandelt.

Das FPGA arbeitet dann genauso wie eine reale, feste digitale Schaltung aus Gattern.

Wichtigstes Merkmal: Parallelität

Anders als ein Mikrocontroller, der Befehle nacheinander ausführt, arbeitet ein FPGA:

- 100 % parallel

- ohne Prozessor

- ohne Programmablauf

Beispiel:

Ein LED-Blinker, ein UART, ein Zähler und ein Filter laufen gleichzeitig, ohne sich gegenseitig zu bremsen.

Warum FPGAs?

Vorteile

- Sehr schnell und deterministisch

- Harte Echtzeit

- Parallelität

- Energieeffizient

- Frei konfigurierbar

- Kann komplexe digitale Systeme umsetzen

- Ideal für:

- Signalverarbeitung

- Kommunikation (UART, SPI, CAN, Ethernet)

- Steuerungen

- Motorregelung

- Audio/Video

- Messsysteme

Nachteile

- Teurer als Mikrocontroller

- Schwerer zu programmieren

- Braucht viel Wissen über digitale Logik

- Große Tools (Quartus, Vivado …)

Was macht ein FPGA besonders?

Ein FPGA kann nach dem Start seine komplette interne Schaltung ändern, weil:

- Die Logikzellen programmierbar sind

- Die Verbindungen programmierbar sind

→ Dadurch können beliebige digitale Schaltungen nachgebildet werden.

Kombinatorische Logik

Was ist kombinatorische Logik?

Wenn man von kombinatorischer Logik spricht, meint man Schaltungen, bei denen der Ausgang direkt von den Eingängen abhängt. Es gibt kein „Merken“ von alten Werten, kein Zwischenspeichern – sobald sich ein Eingang ändert, reagiert der Ausgang sofort. Das ist die Grundlage für einfache Bausteine wie UND‑, ODER‑ oder NICHT‑Gatter, aber auch für komplexere Dinge wie Multiplexer oder Decoder.

VHDL und Kombinatorische Logik

- Direkte Abhängigkeit: In VHDL bedeutet kombinatorische Logik, dass ein Ausgang sofort den Wert bekommt, der sich aus den Eingängen ergibt. Es läuft nicht Schritt für Schritt wie in einem Programm, sondern alles gleichzeitig – genau wie in echter Hardware.

- Direkte Zuweisung: Man schreibt einfach, dass ein Ausgang immer gleich einer bestimmten Verknüpfung der Eingänge ist. Beispiel: „y ist gleich a UND b“. Das ist die einfachste Form.

- Prozesse ohne Takt: Wenn die Logik etwas komplizierter ist, fasst man Bedingungen in einem Prozess zusammen. Wichtig ist, dass dabei kein Clock‑Signal verwendet wird, sonst würde es sequentielle Logik werden. Typisch ist das bei Multiplexern oder Decodern.

- Simulation vs. Hardware: Am Computer sieht man die Änderungen sofort. In einer echten Schaltung dauert es ein kleines bisschen länger, weil das Signal durch Bauteile laufen muss. Diese Verzögerung nennt man Laufzeit.

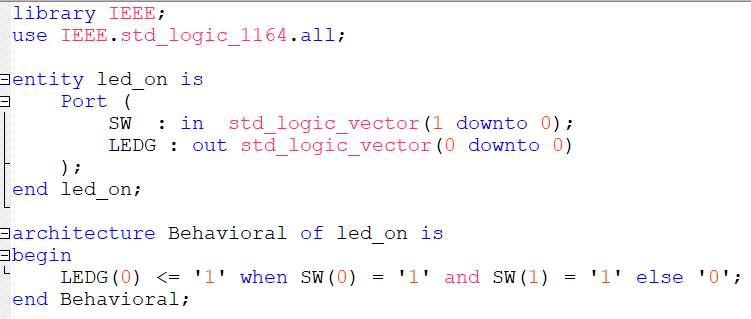

Code Beispiel

Code auf dem DE0-Board

Sequentielle Logik

Sequentielle Logik kurz erklärt:

- Im Gegensatz zur kombinatorischen Logik hängt der Ausgang nicht nur von den aktuellen Eingängen ab, sondern auch von einem gespeicherten Zustand.

- Dieser gespeicherte Zustand entsteht durch Rückkopplung und wird mit einem Taktsignal (Clock) gesteuert.

- Dadurch kann die Schaltung „merken“, was vorher war, und Abläufe Schritt für Schritt ausführen.

Zusammenhang mit VHDL

- In VHDL beschreibt man Sequentielle Logik in Prozessen, die auf den Takt reagieren.

- Das bedeutet: Bei jeder Taktflanke wird überprüft, ob neue Werte übernommen werden sollen.

- So lassen sich Bausteine wie Zähler, Register oder Zustandsautomaten modellieren.

- Der große Unterschied zur kombinatorischen Logik:

- Kombinatorisch = sofortige Reaktion auf Eingänge

- Sequentiell = Reaktion im Takt, mit „Gedächtnis“ für vorherige Werte

Warum ist Sequentielle Logik wichtig?

- Mit kombinatorischer Logik allein könnte man nur einfache Verknüpfungen bauen.

- Erst durch Sequentielle Logik kann man Abläufe, Speicher und komplexe Steuerungen in VHDL beschreiben.

- Damit bildet VHDL die reale Hardware sehr genau ab:

- Kombinatorisch für direkte Verknüpfungen

- Sequentiell für alles, was einen Zustand oder zeitliche Abfolge braucht

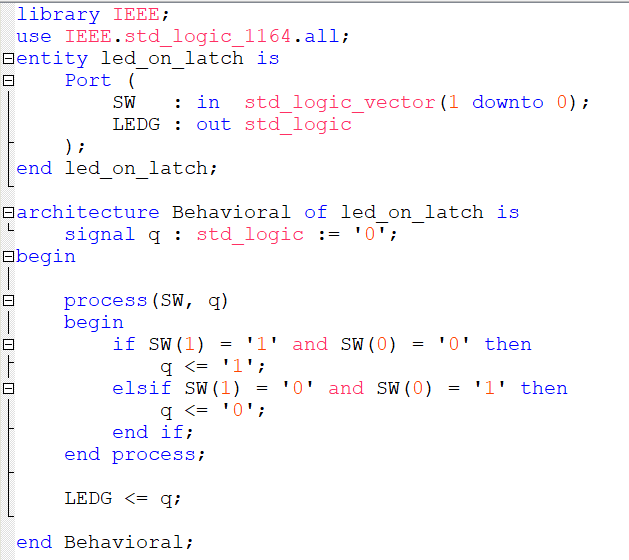

Code Beispiel

Vorgehensweise bei der Simulation von VHDL-Schaltungen

1. Entwurf der VHDL-Schaltung (Design Unit)

Zuerst wird die eigentliche Schaltung beschrieben:

- Entity

- Definiert die Schnittstelle der Schaltung

- Ein- und Ausgänge (Ports)

- Keine Funktionalität

- Architecture

- Beschreibt das Verhalten oder die Struktur

- Logik, Prozesse, Signalzuweisungen

entity and_gate is

port (

A : in std_logic;

B : in std_logic;

Y : out std_logic

);

end and_gate;

architecture rtl of and_gate is

begin

Y <= A and B;

end rtl;

2. Erstellen eines Testbenches

Die Testbench ist wie das "Herz" der Simulation

Zweck:

- Testet die Schaltung ohne echte Hardware

- Liefert Eingangssignale

- Überprüft die Ausgänge

Eigenschaften einer Testbench:

- Keine Ports

- Enthält das zu testende Design (DUT – Device Under Test)

- Erzeugt Stimuli (Testsignale)

Beispiel:

entity tb_and_gate is

end tb_and_gate;

architecture sim of tb_and_gate is

signal A, B, Y : std_logic;

begin

DUT: entity work.and_gate

port map (

A => A,

B => B,

Y => Y

);

stimulus: process

begin

A <= '0'; B <= '0'; wait for 10 ns;

A <= '0'; B <= '1'; wait for 10 ns;

A <= '1'; B <= '0'; wait for 10 ns;

A <= '1'; B <= '1'; wait for 10 ns;

wait;

end process;

end sim;

3. Kompilieren der VHDL-Dateien

- Alle VHDL-Dateien werden vom Simulator analysiert

- Syntax- und Typfehler werden gefunden

- Reihenfolge beachten:

Design → Testbench

Typische Simulatoren:

- ModelSim / Questa

- Vivado Simulator

- GHDL (Open Source)

4. Start der Simulation

- Die Testbench wird gestartet (nicht die Entity!)

- Der Simulator führt die Prozesse zeitgesteuert aus

- "wait for" bestimmt den Zeitverlauf

5. Analyse der Simulationsergebnisse

- Wellenform (Waveform)

- Signale werden als Zeitdiagramm angezeigt

- Man prüft:

- Logische Korrektheit

- Signalverzögerungen

- Taktverhalten

- Vergleich mit Erwartung

- Entspricht das Ergebnis der Wahrheitstabelle?

- Sind Flanken und Zeiten korrekt?

Beispiel:

Zeit → 0ns 10ns 20ns 30ns

A 0 0 1 1

B 0 1 0 1

Y 0 0 0 1

6. Fehlerbehebung (Debugging)

Falls fehler auftreten:

- VHDL-Code anpassen

- Testbench erweitern

- Simulation erneut starten

7. (Optional) Vorbereitung für Synthese

- Nach erfolgreicher Simulation:

- Code auf synthesefähige Konstrukte prüfen

- Keine "wait for" im eigentlichen Design

- Testbench wird nicht synthetisiert

Kurz Zusammengefasst

- Schaltung in VHDL beschreiben

- Testbench erstellen

- Code kompilieren

- Simulation starten

- Wellenformen auswerten

- Fehler beheben

- Design freigeben für Synthese

Der Datentyp std_ulogic (und der Sub-Typ std_logic)

Der Datentyp std_ulogic (und der Sub-Typ std_logic) ist eine Erweiterung von BIT. Dies ist notwendig, um die realen Anforderungen eines HW-Entwurfs zu genügen. Oft sind die Zustände '0' oder '1' nicht ausreichend, Signale können weitere Zustände annehmen – zum Beispiel 'Z' (hochohmig). Nach dem Einschalten kann erstmals ein Signal undefiniert sein, bis ein bestimmtes Ereignis eintritt (zum Beispiel ein Reset). Auch ein Logiksimulator, der einen digitalen Schaltungsentwurf simulieren soll, muss mit mehreren Zuständen arbeiten. Deshalb wurde der Datentyp std_ulogic spezifiziert, der neunwertig ist - Auszug aus dem std_logic_1164

| Wert | Bedeutung |

|---|---|

| 'U' | Uninitialized (nicht initialisiert) |

| 'X' | Forcing Unknown (erzwungen unbekannt) |

| '0' | Forcing 0 (erzwungen 0) |

| '1' | Forcing 1 (erzwungen 1) |

| 'Z' | High Impedance (hochohmig) |

| 'W' | Weak Unknown (schwach unbekannt) |

| 'L' | Weak 0 (schwach 0) |

| 'H' | Weak 1 (schwach 1) |

| '-' | Don't care (egal) |

Da std_ulogic nicht Teil der VHDL Sprache ist, sondern in Form einer Bibliothek vorliegt, muss diese Bibliothek vor Verwendung eingebunden werden.

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

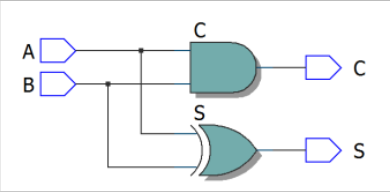

→ Beispiel: Halbaddierer unter Verwendung des Datentyp std_ulogic

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity HA is

port ( A, B: in std_ulogic;

S, C: out std_ulogic

);

end HA;

architecture Architektur of HA is

begin

S <= A xor B; -- Summe

C <= A and B; -- Uebertrag

end Architektur;

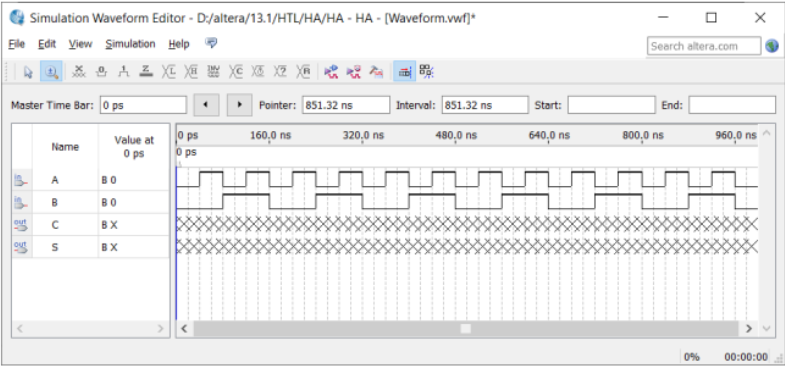

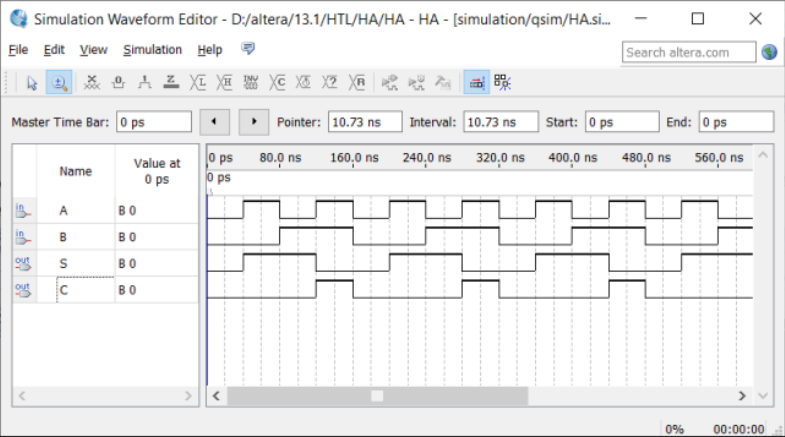

Das Ergebnis wird mittels Simulation überprüft. Zur Erstellung gibt es zwei Wege… (halb-)automatisch (ähnlich wie bei Altium) oder graphisch. Wir werden zu Beginn das Testfile graphisch erstellen: File → New → Verification/Debugging Files → University Program VWF. Ein Grahik-Editor wird geöffnet; im ersten Schritt fügen wir die Ein- und Ausgangssignale hinzu und legen dann im zweiten Schritt das Eingangsbitmuster fest:

Mit File → Save wird der Entwurf gespeichert, wobei der vorgeschlagene Name (→ hier Waveform.vwf) nicht verändert wird. Mit Klick auf wird die RTL Simulation (= funktionale Simulation) gestartetS ist log. 1 wenn A oder B (aber nicht gleichzeitig!) log. 1 ist, C ist log. 1 wenn A und B log. 1 sind… somit wurde die korrekte Funktion des Halbaddierers per Simulation überprüft!

S ist log. 1 wenn A oder B (aber nicht gleichzeitig!) log. 1 ist, C ist log. 1 wenn A und B log. 1 sind… somit wurde die korrekte Funktion des Halbaddierers per Simulation überprüft!

Blockhierarchie in VHDL

In VHDL beschreibt man digitale Schaltungen nicht als ein einziges großes Ganzes, sondern man zerlegt sie in Blöcke. Jeder Block ist ein klar abgegrenzter Teil der Schaltung mit definierten Ein- und Ausgängen.

Diese Blöcke werden dann hierarchisch angeordnet:

- Ganz oben steht der Top-Level-Block (das gesamte System).

- Darunter liegen Unterblöcke, die bestimmte Funktionen übernehmen.

- Diese Unterblöcke können wiederum aus kleineren Blöcken bestehen.

- Am Ende stehen die Grundbausteine wie logische Gatter oder Flip-Flops.

Aufbau eines Blocks

Ein Block hat zwei zentrale Aspekte:

- Entity (Schnittstellen) → beschreibt, welche Signale hinein- und hinausgehen.

- Architecture (Innenleben) → beschreibt, was im Block passiert.

Dadurch ist jeder Block wie ein Baustein mit klarer Funktion.

Wie entsteht die Hierarchie?

- Der Top-Level-Block definiert die äußeren Anschlüsse des Systems (z. B. Takteingang, Datenleitungen).

- Innerhalb dieses Blocks werden Unterblöcke eingebaut.

- Jeder Unterblock hat wiederum seine eigene Schnittstelle und sein eigenes Innenleben.

- Die Signale werden von oben nach unten durch die Hierarchie weitergereicht.

Man kann sich das wie eine Firma vorstellen:

- Oben die Leitung (System).

- Darunter Abteilungen (Unterblöcke).

- Darunter Mitarbeiter (kleinere Bausteine).

Warum ist das wichtig?

- Übersichtlichkeit: Große Systeme bleiben verständlich.

- Modularität: Jeder Block ist für sich abgeschlossen und kann wiederverwendet werden.

- Testbarkeit: Man kann einzelne Blöcke separat simulieren und prüfen.

- Flexibilität: Änderungen betreffen nur den betroffenen Block, nicht das ganze System.

Ende

Du hast das Tutorial durchlaufen!